# Design and implementation of multiport memories for re configurable devices

Arun S.Tigadi, Deepti. S.P, Hansraj Guhilot.

**Abstract**— The included block RAMs in the fabric have typically only two ports, so the multi-ported memories have become challenging to implement with FPGAs. Only by using logic elements or by combination of multiple block RAMs, the multi-ported memories can be designed. A new design is proposed in this paper called Live Value Table. This design has more number of read ports and write ports compared to other methods. The other method called XOR based approach is also introduced ,this requires more area compared to Live Value Table based approach.

\_\_\_\_

Index Terms— FPGA, memory, multi-port, multipumping, LVT, XOR.

## **1 INTRODUCTION:**

Designers increasingly use FPGAs to implement the larger and more complex systems-on-chip as these FPGAs continue to increase in their transistor density. Frequent sharing, communication, queueing and synchronization among distributed functional units and compute nodes are required by these complex designs. The construction of multi-ported memories of FPGA logic elements is inefficient and is one of the challenge. And the block RAMs with only two ports are provided by the FPGA substrate. However , the multi-ported memories with more than two ports must be SOFT that is constructed using logic elements and/or hard BRAMs.

Multi-ported memories have become challenging to implement with FPGAs as the block RAMs provided typically have only two ports. Here in this paper a thorough exploration of the design of FPGA based soft multi-ported memories is presented by evaluating conventional solutions to this problem and a new design is introduced here that combines block RAMs into multi-ported memories with more number of read and write ports called Live Value Table. And also another approach which is based on XOR operation which provides multi-ported memories that uses less logic than LVT design but with more block RAMs. Along with this LVT and XOR methods, other methods such as Replication, Banking and multi-pumping are designed and implemented. And their respective area, timing, power values of all methods are compared for different devices.

In VLSI systems, multi-ported memories are commonly used components such as register files in microprocessors, storage media or network applications. And through different ports, the content of a multiported memory can be accessed simultaneously. For processors like speed, media and communication processors, this multi-ported memory is especially valuable. Since all ports need to be verified, these multiported memories require more testing effort.

# **2 IMPLEMENTATION**

## 2.1 Replication :

\_\_\_\_\_

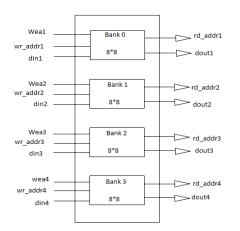

Replication is nothing but a process of making a replica or a copy of something. Here in this project it includes only one external write port with four number of external read ports. Only one single write port is connected to one of the four ports of each replicated RAM. This method is one of the simplest method to increase the number of read ports of a memory and also gives as many as copies of the memory as the read ports are required that is by keeping the common write address and data as shown in fig (a), the whole memory bank is replicated in order to provide more number of read ports. And to all the copies of this memory only one write port is routed to maintain them up to date. Hence this technique alone does not support for more than one write port. At the same address, all the bank replicas will be written with any data. Hence reading from any bank is equivalent. This replication requires more area and more power is consumed.

Figure 1(a) Replication

## 2.2 Banking :

This banking method is different compared to replication method. This method supports any number of read and write ports. Here the 32\*8 memory location is divided among all multiple banks. As the four ports are considered, the 32\*8 is divided into four 8\*8. That is each bank will have memory location of 8\*8 as shown in above fig(b). These additional banks formed will support the additional read and write port, that is only one corresponding section can only be accessed by each write port and read port. But like replication, this method cannot access memory between the memory banks. Only the corresponding memory bank is accessed by its particular read or write port. Hence this design does not support the sharing between the ports. To create truly multi-ported memory, this method needs to be combined with any other methods. This is one of the simplest method to design. As compared to replication, this method requires less area space.

Figure 1(b) Banking

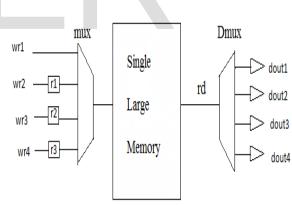

## 2.3 Multipumping :

To control the processing of the memory location access, this method makes use of an external clock which is the multiple speed of the system clock. This design requires multiplexers and registers to hold the address and data temporarily, of the pending reads and writes. Here there is no doubling or sharing of memory like in replication and banking, there is only one single large memory. Before and after the memory, there are registers and multiplexers to multiplex the read or write operations. The write address is written in the memory, before writing, the write address are being multiplexed using the select lines of multiplexer. All the write addresses are written with priority, the first write address in figure(c) has the first priority, so the remaining three write address ports have the registers which holds the temporary address and data of the pending ports. The address which are stored in memory are read using the select lines of the Dmux and are read at the corresponding output. This method has main advantage that it can simultaneously read and write the data. Also this approach requires less space. The main drawback of this method is with the increase in number of ports, the external operating frequency gets reduced.

Figure 1(c) Multipumping

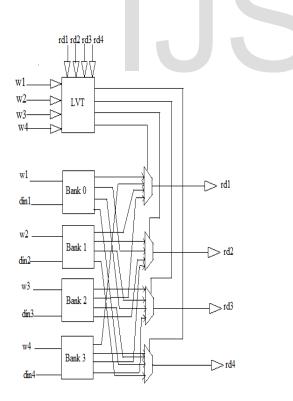

## 2.4 Live Value Table:

The LVT is a new design which is introduced for the true multi-ported memories that provides the more better area scaling compared to other approaches. And has the higher frequencies compared to multipumping method. This LVT is nothing but a small multi-ported memory. This is somewhat similar to replication. Writing is exactly like replication, but it has a separate LVT module which stores the latest vaues. For each write address, the LVT stores the bank number which holds the most recent data.

An LVT based multi-ported memory makes use of different replication of banks for each write address port but each bank has many read address ports. All the read address are accessed parallel by all the banks. And the LVT module uses the multiplexers that helps to read out the correct bank number which it holds the most recently written bank number for each of the address. A banked design is allowed by this method to behave like a true multi-ported memory by which appropriate banks are directed by reads based on that bank holds the most latest or live write data. This LVT module has a same memory depth as that of the depth of the memory bank. This is one of the main cause of more area space. Compared to the actual memory banks, the LVT is much narrower as rather storing the whole data, it stores or holds only the bank numbers.

Figure 1(d) Live Value Table

So this LVT based multi-ported memories is more efficient compared to other approaches. The only basic idea of this design is that each read port should be able to connect to the most latest updated written bank for the memory location given. There are two challenges which are caused in this LVT based design by the togetherness of the LVT module itself and the multiplexers which are at the output side. They are : critical path is constituted and for implementation requires more number of logic elements. These challenges are avoided by the method which is explained in the next section.

## 2.5 XOR -Based Design:

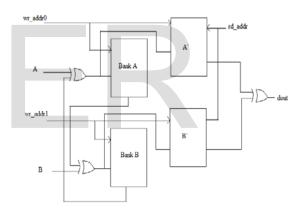

This XOR (exclusive OR) is the logical operation. The outputs are true only when the two inputs have different values. When both the inputs are of same values then the output results false.

## Figure 1(e) XOR Based Design

The truth table for this operation is shown below:

| Input | s | Outputs |

|-------|---|---------|

| Α     | В |         |

| 0     | 0 | 0       |

| 0     | 1 | 1       |

| 1     | 0 | 1       |

| 1     | 1 | 0       |

The XOR operation has the following properties:

- $A \wedge 0 = A$

- $B \wedge B = 0$

- $A \wedge B \wedge B = A$

The third property indicates that the two values A and B can be XORed together , and by XORing the result A<sup>A</sup>B with B, the value A can be recovered. Here a simple memory 2W/1R is constructed as shown in figure(e). As illustrated in the figure, there are two BRAMs as the write ports each has its own bank. And to both the BRAMs each writes are copied that is the same value is written in all the BRAMs of the corresponding locations. The value A is stored by the Wo write port to some location, now this value A is XORed with the value of bank B of the corresponding location as of bank A. Similarly, the value B is stored by W1 write port to lower location of bank B, this value B is XORed with the value of the corresponding location of bank A. The main goal of this design for the read port is that it should only consist of the XOR values of the memory bank outputs. And this goal is achieved by storing the XORed values in their respective separate banks that is A` and B` as shown in the above design. And at the end, the stored values are XORed again. So that should result in recovering the value of A.

#### 3. RESULTS :

The results part includes the simulation and chipscope results of all the five methods.

#### 3.1 Replication:

(a) write operation

| Ban Signal<br>onts<br>ont#<br>ont# | Vatue<br>71<br>32      |

|------------------------------------|------------------------|

| out)<br>out)                       | 32                     |

| out3                               |                        |

|                                    |                        |

|                                    | 33                     |

| put4                               | 34                     |

|                                    | 0                      |

| vite address                       |                        |

|                                    | 35                     |

| atrel                              | 01                     |

| otrw2                              | 02                     |

| airel                              | 03                     |

| dirad                              | 04                     |

|                                    |                        |

|                                    | in<br>Markal<br>Markal |

#### (c) Chipscope results

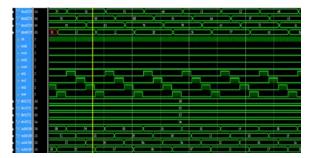

The above screenshots are the simulation results of the replication which includes write and read operations. When the write enable is 1, the data din is written in to write address as shown in figure. And when write enable becomes zero, the address are read in output i.e dout. The same read and write operations are shown for all methods below in the screenshots. And this also includes screenshot of chipscope results.

#### 3.2 Banking :

#### (a) write operation

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      | 25.4         |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|-------------|-------|-------|----------|----------------|----|--------|--------|-------|-------|--------|-------|------------|-------|------|--------------|----------|---------------|------|-----------|---------|---------|--------|-------|----------|-----|-------|--------|------|---------|--|

|             |       |       |          |                |    |        |        |       |       |        |       |            |       | . 1  | CO -#        |          |               | . P  | 20.44     |         |         | 700 HE |       |          | _   | 00 T  |        |      | 500 re  |  |

|             |       |       |          |                | х  |        |        |       | X     |        |       |            |       | -    | -            |          | -             |      | -         | -       |         |        |       |          |     | _     |        |      | <u></u> |  |

|             |       |       |          |                |    |        |        |       |       |        |       | <u>. (</u> |       | ŧŤ   |              | -        | λ             | -    |           |         |         | 1801   |       | <u>.</u> | -   |       | P      |      |         |  |

|             |       |       |          |                |    | -~     |        | _     |       |        |       | v ar       |       | 17   |              | <u>.</u> |               |      |           | ÷.,     |         |        |       |          |     |       |        |      |         |  |

|             |       | 1 I I |          | <u> </u>       | 10 |        |        | -     |       |        |       | 14         | -     | Τt   |              |          | All of        |      |           |         |         | 1      |       | ~        |     |       |        |      |         |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       | -     |          |                |    |        |        |       |       |        |       |            |       | 11   |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       | -     |          |                | -  |        |        |       |       |        |       |            |       | 11   |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       |       |          |                | -  |        |        |       |       |        |       |            |       | 11   |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       |       |          | -              | -  | M Volt | No Van | Viel  | 3.005 | i line | 100   | 740        | i a   | 5    | <b>T</b> Y # | Viz      | <b>TEST</b>   | 11   | d V in    | V a V   | in Vill | Vax.   |       |          | e V | ar.   | V HO   | BY H |         |  |

|             |       |       |          |                | =6 | 10 000 | 11 (11 | Yan   |       | 1 10   |       | -          | iii Y | Ð    | <b>1</b> 14  | Ŷī       | in the second |      | 10 100    | Fig.    |         | 1000   | d ( 1 | 16       |     | 10.11 | i an   | 60 0 |         |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       | -     | _        | 60             | -  | -      | -      | Y a   |       |        | i m   | æ          | mV    | ie i |              | No.      |               | m Vi | n m       | 3       |         |        |       |          |     | -     |        | -    |         |  |

|             | -     |       | V of     | i an           | _  |        |        | 71-04 |       |        | 100.0 | 1.080      | 0.03  |      |              |          |               | =    | PLA LINES | 1.30.21 |         | 1000   |       | 0.000    |     |       | 0 6863 |      | 5       |  |

|             |       | 4 6   | ¥ 101    | i ani          |    |        |        |       |       |        |       |            |       |      |              |          | - No          |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          | 107           |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

| 2. 40192 41 | -     |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

|             | 104   |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          | -             |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

|             | 100   | 4     | a kate   | $\mathbf{x} =$ |    |        |        |       |       |        |       |            |       |      |              | e        | -             |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

|             | 100   |       | S X III  | ΪX –           |    |        |        |       |       |        |       |            |       |      |              |          | -             |      |           |         |         |        |       |          | _   |       |        |      | 5       |  |

|             | HOR H |       | -        | Ιx.            |    |        | _      |       |       |        |       |            |       |      |              |          | _             |      |           |         |         |        |       |          |     |       |        |      | 5       |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       | T    |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             |       |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

|             | -     |       |          |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

| 10.95.75 m  |       |       | 1.446.76 |                |    |        |        |       |       |        |       |            |       |      |              |          |               |      |           |         |         |        |       |          |     |       |        |      |         |  |

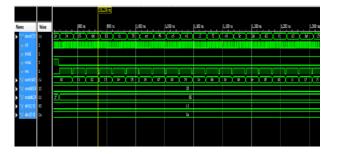

(b) read operation

(c) Chipscope Results

(c) Chipscope Results

# **3.3 Multipumping :**

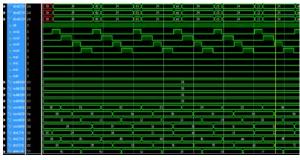

(a) write operation

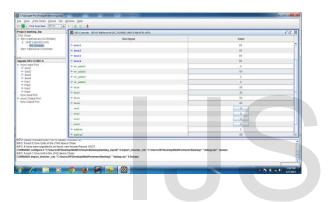

3.4 Live Value Table :

(a) write operation

| ee [                                                                                   | Value       |    | 1,200 m |    |    | ičes – |   | 146.0 |      | 1.500 - |                 | 1.60     |    | 1,700 10 |          | 1.82 |          |    | 100 m |             | 2.80 |      |

|----------------------------------------------------------------------------------------|-------------|----|---------|----|----|--------|---|-------|------|---------|-----------------|----------|----|----------|----------|------|----------|----|-------|-------------|------|------|

| / Date:                                                                                | 12          |    |         | X  | ¥. | X      |   | T)    |      | DX.     | 12              | (        |    | k        | Ξ)C      | 77   | <b>)</b> |    | ٥     | X           | 16   | ) i  |

| 4 10425                                                                                | <i>(</i> 2  |    | 94      |    | k  | . 19   | t | 0     | ( 61 | Dø      |                 |          | 44 | Y        | 8        |      | 24       |    | 45    |             | 6    |      |

| 1000                                                                                   | 8c          | 24 |         | 1  |    |        |   | ¢.    |      | 1       |                 |          | ų  | Ξx       | đ        | DC   | 20       | 15 | 1     | ) M         |      | 0    |

| 10471                                                                                  | £1          | 24 |         |    |    | 8 6    | 0 |       | (    | DC      | 20              |          |    | k.       | <b>6</b> | . 0  |          | 65 |       | $) \square$ | 6    |      |

|                                                                                        | 1           |    |         |    |    | 10     |   |       |      |         | alle i di di di |          |    |          |          |      |          |    |       |             |      | T. I |

|                                                                                        | 1           |    |         |    | -  |        | - |       |      | -       |                 |          |    | -        |          |      |          | _  |       |             | _    |      |

| ana?                                                                                   | 1           |    |         |    |    |        |   |       |      | -       |                 |          |    | _        |          |      |          | _  |       |             |      |      |

|                                                                                        | 1           |    |         |    | -  |        | - | -     |      | -       |                 | -        |    | _        |          | -    |          | _  |       |             | -    |      |

|                                                                                        |             |    |         |    |    |        |   |       |      |         |                 |          |    |          |          |      |          |    |       |             |      |      |

|                                                                                        | 1           |    |         | _  |    |        | - | -     |      | -       |                 |          |    | _        |          |      |          | _  |       | _           |      |      |

|                                                                                        | 3           | л  |         | n  |    |        |   | Ŀг    |      |         |                 | <u> </u> |    |          |          |      | 1        |    |       | Л           |      |      |

|                                                                                        |             | -  |         | n, | t  |        |   | F     | F    |         |                 | 7        |    | h        |          | m_   | 2        | 7  |       | -           | t    | -    |

|                                                                                        |             | -  |         | 1  | Ļ  |        | 7 |       |      |         |                 |          |    | 5        |          | -    |          | }  |       | -           | h    |      |

|                                                                                        | 1           |    |         |    |    |        |   |       |      |         |                 |          | h  |          |          |      |          | ]- |       |             | 7    |      |

| 1996<br>1911<br>1913<br>1914<br>1916<br>1916<br>1916                                   | 3 1 3 1 2 2 |    |         |    |    |        |   |       |      |         |                 |          |    | •        |          |      |          |    |       |             |      |      |

| <br><br><br><br><br><br>                                                               | 25          |    |         |    |    |        |   |       |      |         |                 |          |    |          |          |      |          |    |       |             |      |      |

| 11<br>15<br>11<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14 | 15<br>26    |    |         |    |    |        |   |       |      |         |                 |          |    |          |          |      |          |    |       |             |      |      |

| 41.<br>41.<br>43.<br>43.<br>43.<br>43.<br>43.<br>43.<br>43.<br>43.<br>43.<br>43        | 25          | *  |         |    |    |        |   |       |      |         |                 |          |    |          |          |      |          |    |       |             |      |      |

(b) read operation

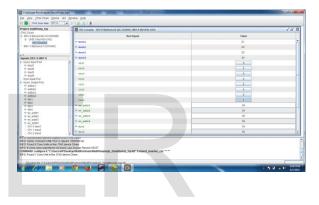

3.5 XOR :

(a) Write operation

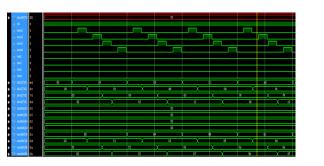

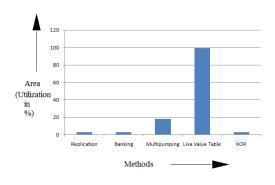

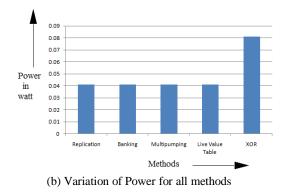

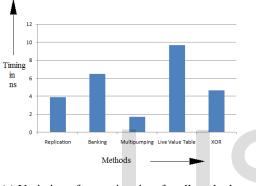

**GRAPHS**:

(a) Area utilization versus all methods

| Depth | Slices | BRAMs |

|-------|--------|-------|

| 2     | 2      | 4     |

| 4     | 4      | 4     |

| 8     | 6      | 4     |

| 16    | 8      | 4     |

| 32    | 10     | 4     |

| 64    | 10     | 4     |

(c) Variation of execution time for all methods

| Depth | Slices      | BRAMs |

|-------|-------------|-------|

| 2     | 2           | 4     |

| 4     | 4           | 4     |

| 8     | 6           | 4     |

| 16    | 6           | 4     |

| 32    | 6           | 4     |

| 64    | 6           | 4     |

|       | (b) Banking |       |

The above graphs includes the plotting of area, power,timing for all the different methods for the spartan 3E family. It includes variation of area utilization, power and run time for all the five methods.

The below tables shows the number of slices and BRAMs used for different depths for all the five methods :

As the depth of the memory increases, the number of slices increases or remains same sometimes with each increase in depth as shown in the tables below and above

| Depth | Slices | BRAMs |

|-------|--------|-------|

| 2     | 42     | 1     |

| 4     | 44     | 1     |

| 8     | 45     | 1     |

| 16    | 51     | 1     |

| 32    | 57     | 1     |

| 64    | 57     | 1     |

(c) Multipumping

| Depth | Slices | BRAMs |

|-------|--------|-------|

| 2     | 285    | 4     |

| 4     | 300    | 4     |

| 8     | 319    | 4     |

| 16    | 324    | 4     |

| 32    | 334    | 4     |

| 64    | 337    | 4     |

(d) LVT

| Depth | Slices | BRAMs |

|-------|--------|-------|

| 2     | 18     | 4     |

| 4     | 19     | 4     |

| 8     | 20     | 4     |

| 16    | 24     | 4     |

| 32    | 25     | 4     |

| 64    | 25     | 4     |

(e) XOR

## 4. Conclusion :

The Live Value Table and XOR based approaches have been introduced which are fastest among the other conventional approaches like replication, banking and multipumping. These conventional methods either have inefficient area or slow. So the Live Value Table and XOR approaches are introduced that behaves like a true multi-ported design.

#### **REFERENCES:**

[1] Implementing Multi-Port Memories in ProASICPLUSDevices.http://www.actel.com/document s/APA\_MultiPort\_AN.pdf, July 2003. Application Note AC176, Accessed Sept. 2009.

[2] Mercury Programmable Logic Device Family Data Sheet.http://www.altera.com/literature/ds/ dsmercury.pdf, Jan 2003. Version 2.2, Accessed Sept. 2009.

[3] Stratix III Device Handbook Volume 1, Chapter 4: TriMatrix Embedded Memory Blocks in Stratix III Devices.http://www.altera.com/literature/hb/stx3/stx3\_siii5 1004.pdf,May 2008. Version 1.8, Accessed Sept. 2009.

[4] Advanced Synthesis Cookbook: A Design Guide for Stratix II, Stratix III, and Stratix IV Devices.http://www.altera.com/literature/manual/stx\_co okbook.pdf, July 2009. Version 5.0, Accessed Nov. 2009.

aches other g and